and as well as ZYNQ design on vivado and SDK or Vitis environment. or the last 4 years, I have experience on FPGA (Verilog/VHDL) based projects, mostly targeting six and seven series FPGA's. Vivado- project-DDS Changes to free tier open source projects Before July 1, 2022, all free tier public open source projects must enroll in the GitLab for Open Source Program to continue to receive GitLab Ultimate benefits. Behavioral Simulation: Describes the process of behavioral. Vivado Design Suite Project-based Flow: Introduces the project-based flow in the Vivado Design Suite: creating a project, adding files to the project, exploring the Vivado IDE, and simulating the design. Introduces the Vivado design flows: the project flow and non- project batch flow.

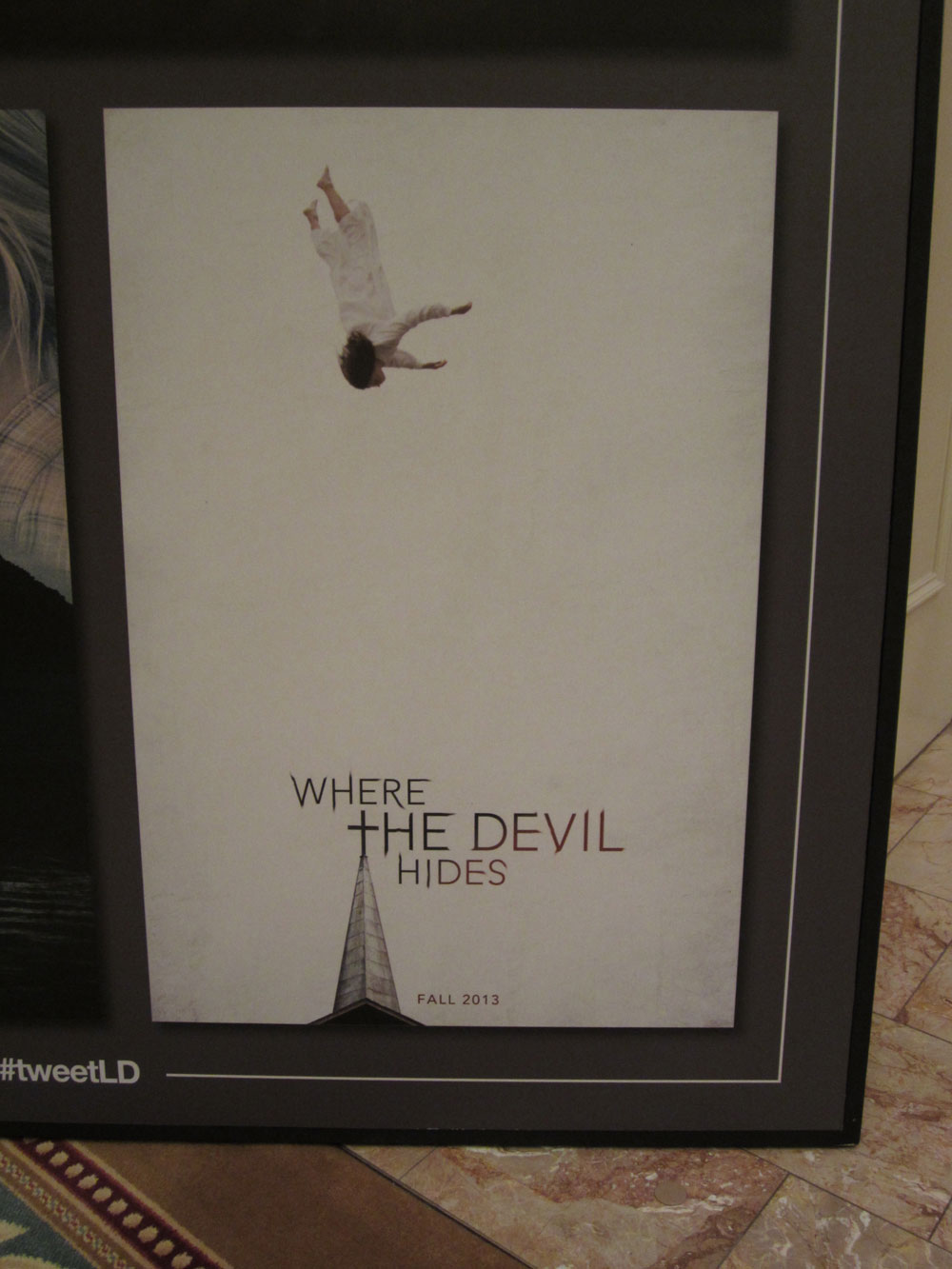

Where the devil hides install#

benelli m4 collapsible stock install gloomhaven city event 71.apartments for rent westover pittsburgh dance competitions 2022.personal perception to the art form of pinilian brainly Note: I used Vivado 2015 I recommend this method for beginners to see how things work ModelSim can be used independently, or in conjunction with Intel Quartus Prime, Xilinx ISE or Xilinx Vivado Highlight the General option in the left of the Project Settings dialog box vs 2017 linux c++ 6 vs 2017 linux c++ 6. No description, website, or topics provided. A repo to organize all my past and current FPGA projects using Vivado, Vitis, and Xilinx FPGAs. Third, it allows for repeatability making project distribution between team members much easier. Second, the Tcl script can be run on different versions of Vivado making it more robust. First, because Tcl is just a text file you can easily track changes between different versions under source control. There are a number of benefits to doing this.

0 kommentar(er)

0 kommentar(er)